## SEMICONDUCTOR DEVICE AND ITS MANUFACTURING METHOD

| Patene number.           | 001168231<br>I-06-22                                                                                     |

|--------------------------|----------------------------------------------------------------------------------------------------------|

| Inventor: SAW            | VARA RYUICHI; KAINO NORIYUKI; SHIMOISHIZAKA NOZOMI; NAKAMURA YOSHIFUMI; KUMAKAWA TAKAHIRO; WATASE KAZUMI |

| Applicant: MAT           | SUSHITA ELECTRONICS CORP                                                                                 |

| Classification:          |                                                                                                          |

| - international: H01L    | L21/60; H01L23/12; H01L21/02; H01L23/12; (IPC1-7): H01L23/12; H01L21/60                                  |

| - european:              |                                                                                                          |

| Application number: JP19 | 9990352757 19991213                                                                                      |

| Priority number(s): JP19 | 9990352757 19991213                                                                                      |

## Abstract of JP2001168231

Abstract of JP2001169231 PROBLEM TO BE SOLVED: To provide a semiconductor device that can protect a semiconductor chip from mechanical shock and is highly reliable at low manufacturing costs. SOLUTION: A semiconductor device 100 is provided with a semiconductor component with a main surface 10a where an element electrode 11 is arranged and a side surface 10b, an insulation layer 20 that is formed on the main surface 10a and the side surface 10b, a wiring layer 33 that is formed on the insulation layer 20 and is electrically connected to the element electrode 11, and an external electrode 32 that is formed as one portion of the wiring layer 33 on the insulation layer 20. The semiconductor device 100 is configured so that it can be manufactured as a wafer level CSP and the side surface 10b of the semiconductor component 10 is protected by the insulation layer 20. of the semiconductor component 10 is protected by the insulation layer 20.

Report a data error here

Data supplied from the esp@cenet database - Worldwide

\_.. \_.\_ .

## (12) 公開特許公報(A)

(11)特許出願公開番号 特開2001-168231

(P2001-168231A)

(43)公開日 平成13年6月22日(2001.6.22)

| (51) Int.Cl. <sup>7</sup> |       | 酸別記号 | ΓI   |       | テーマコード( <b>参考)</b> |

|---------------------------|-------|------|------|-------|--------------------|

| H01L                      | 23/12 |      | H01L | 21/60 | 311S 5F044         |

|                           | 21/60 | 311  |      | 23/12 | L                  |

審査請求 未請求 請求項の数28 OL (全 15 頁)

| (21)出顧番号 | 特顧平11-352757            | (71)出顧人 | 000005843           |

|----------|-------------------------|---------|---------------------|

|          |                         |         | 松下電子工業株式会社          |

| (22)出顧日  | 平成11年12月13日(1999.12.13) |         | 大阪府高槻市幸町1番1号        |

|          |                         | (7?)発明者 | 佐原隆一                |

|          |                         |         | 大阪府高槻市幸町1番1号 松下電子工業 |

|          |                         |         | 株式会社内               |

|          |                         | (72)発明者 | 戒能 憲幸               |

|          |                         |         | 大阪府髙槻市幸町1番1号 松下電子工業 |

|          |                         |         | 株式会社内               |

|          |                         | (74)代理人 | 10007/931           |

|          |                         |         | 弁理士 前田 弘 (外1名)      |

|          |                         |         |                     |

|          |                         |         |                     |

|          |                         |         |                     |

(54)【発明の名称】 半導体装置およびその製造方法

(57)【要約】

【課題】 機械的な衝撃から半導体チップを保護するこ とができ、信頼性を向上させた半導体装置を低い製造コ ストで提供する。

【解決手段】 素子電極11が配列された主面10aと 側面10bとを有する半導体素子10と、主面10a上 および側面10b上に形成された絶縁層20と、絶縁層 20上に形成され、素子電極11と電気的に接続された 配線層33と、配線層33の一部として絶縁層20上に 形成された外部電極32とを備える半導体装置100で ある。半導体装置100は、ウェハレベルCSPとして 製造可能な構成をしており、絶縁層20によって半導体 素子10の側面10bが保護された構成をしている。

最終頁に続く

【特許請求の範囲】

【請求項1】 素子電極が配列された主面と、前記主面 の外縁を規定する側面とを有する半導体素子と、

前記半導体素子の前記主面上および前記半導体素子の前 記側面上に形成され、前記素子電極を露出する開口部を 有する絶縁層と、

前記絶縁層上に形成され、前記開口部内において前記素 子電極と電気的に接続された配線層と、

前記配線層の一部として前記絶縁層上に形成された外部 電極とを備える半導体装置。

【請求項2】 前記半導体素子の前記主面に対向する裏 面上に形成された樹脂層をさらに有する請求項1に記載 の半導体装置。

【請求項3】 前記絶縁層および前記樹脂層は、同一の 絶縁性樹脂材料から形成されている請求項2に記載の半 導体装置。

【請求項4】 前記樹脂層は、導電性樹脂層である請求 項2に記載の半導体装置。

【請求項5】 前記導電性樹脂層は、前記素子電極の一 部に電気的に接続されている請求項4に記載の半導体装 置。

【請求項6】 前記樹脂層は、前記半導体素子の前記裏 面の一部を露出する開口部を有している請求項2から5 の何れか一つに記載の半導体装置。

【請求項7】 前記樹脂層は絶縁性樹脂層であり、前記 絶縁性樹脂層上に形成された金属層をさらに備える請求 項2に記載の半導体装置。

【請求項8】 前記配線層は、前記側面上に位置する絶縁層上に形成された側面配線層を有し、

前記金属層は、前記側面配線層に電気的に接続されている請求項7に記載の半導体装置。

【請求項9】 前記金属層は、一部が外部電極として機能する金属配線層である請求項8に記載の半導体装置。

【請求項10】 前記外部電極に接合された金属ボール をさらに有する請求項1から9の何れか一つに記載の半 導体装置。

【請求項11】 前記外部電極上に形成された導電性突 起をさらに有する請求項1から9の何れか一つに記載の 半導体装置。

【請求項12】 前記半導体素子の前記主面に形成さ

れ、前記素子電極を露出する開口部を有するパッシベー ション膜をさらに備え、

前記絶縁層は、前記パッシベーション膜上に形成されて いる請求項1から11の何れか一つに記載の半導体装 置。

【請求項13】 前記半導体素子は、半導体ウェハ内に 形成された半導体チップである請求項1から12の何れ かに記載の半導体装置。

【請求項14】 前記半導体素子は、半導体ウェハから 分離された半導体チップである請求項1から12の何れ かに記載の半導体装置。

【請求項15】 素子電極が配列された主面を有する複数の半導体素子が形成された半導体ウェハを用意する工程と、

前記複数の半導体素子のそれぞれの前記主面の外縁を規 定する側面を露出する溝を前記半導体ウェハに形成する 工程と、

前記溝内に露出した前記側面と前記主面との上に、前記 素子電極を露出する開口部を有する絶縁層を形成する工 程と、

前記開口部に露出した前記素子電極に電気的に接続され る配線層であって、その一部が外部電極として機能する 配線層を、前記絶縁層上に形成する工程と、

前記主面に対向する裏面を研磨することによって、前記 側面上に形成された絶縁層を前記裏面から露出させる工 程とを包含する半導体装置の製造方法。

【請求項16】 研磨された前記裏面に樹脂層を形成す る工程をさらに包含する請求項15に記載の半導体装置 の製造方法。

【請求項17】 前記半導体素子の前記主面を保護する ために使用するバックグラインドテープを前記主面に接 着させた後、前記半導体素子の前記裏面を研磨し、

前記バックグラインドテープを前記主面に接着させた前 記半導体素子の前記裏面に前記樹脂層を形成する請求項 16に記載の半導体装置の製造方法。

【請求項18】 前記半導体素子の前記主面を保護する ために使用するプレートを前記主面に接着剤を介して接 着させた後、前記半導体素子の前記裏面を研磨し、

前記プレートを前記主面に接着させた前記半導体素子の 前記裏面に前記樹脂層を形成する請求項16に記載の半 導体装置の製造方法。

【請求項19】 前記絶縁層および前記樹脂層を同一の 絶縁性樹脂材料から形成する請求項16から18の何れ かひとつに記載の半導体装置。

【請求項20】 前記樹脂層として導電性樹脂層を形成 する請求項18に記載の半導体装置の製造方法。

【請求項21】 前記樹脂層に、前記裏面の一部を露出 する開口部を形成する工程をさらに包含する請求項16 から20の何れか一つに記載の半導体装置の製造方法。

【請求項22】 前記配線層として、前記半導体素子の 前記側面上に位置する絶縁層上に形成される側面配線層 を有する配線層を形成し、

前記裏面を研磨することによって、前記側面配線層を前 記裏面から露出させ、

前記裏面に形成する樹脂層として、前記側面配線層を露 出する開口部を有する絶縁性樹脂層を形成し、

前記開口部内に露出した前記側面配線層に電気的に接続 される金属層を前記絶縁性樹脂層上に形成する請求項1 6から19の何れか一つに記載の半導体装置の製造方 法。 【請求項23】 前記金属層として、一部が外部電極として機能する金属配線層を形成する請求項22に記載の 半導体装置の製造方法。

【請求項24】 前記配線層を形成する工程の後に、前記絶線層上に形成され、前記配線層を被覆し、且つ前記外部電極の一部を露出するソルダーレジスト層を形成する工程をさらに包含する請求項15から23の何れか一つに記載の半導体装置の製造方法。

【請求項25】 前記金属配線層を形成する工程の後 に、前記絶縁性樹脂層上に形成され、前記金属配線層を 被覆し、且つ前記外部電極の一部を露出するソルダーレ ジスト層を形成する工程をさらに包含する請求項23ま たは24に記載の半導体装置の製造方法。

【請求項26】 前記外部電極上に金属ボールを接合す る工程をさらに包含する請求項15から25の何れか一 つに記載の半導体装置の製造方法。

【請求項27】 前記外部電極上に導電性突起を形成す る工程をさらに包含する請求項15から25の何れかに 記載の半導体装置の製造方法。

【請求項28】 前記裏面から絶縁層を露出させる工程 より後に、前記半導体ウェハを前記複数の半導体素子の それぞれに分離する工程をさらに包含する請求項15か ら27の何れか一つに記載の半導体装置の製造方法。

【発明の詳細な説明】

[0001]

4

【発明の属する技術分野】本発明は、半導体素子を備え た半導体装置およびその製造方法に関する。特に、半導 体素子を保護し、外部装置と半導体素子との電気的な接 続を確保する半導体装置およびその製造方法に関する。 【0002】

【従来の技術】近年、半導体集積回路装置(以下、「半 導体装置」と称する。)を搭載した電子機器の小型化及 び低価格化の進展は目ざましく、これに伴って、半導体 装置に対する小型化及び低価格化の要求が強くなってい る。

【0003】半導体装置の小型化の要求に対して、半導体ウェハから切り出した半導体チップ(ベアチップ)の サイズでパッケージを施した半導体装置(以下、このパ ッケージ形態または半導体装置を「CSP(チップ・サ イズ・パッケージ)」と称する。)が開発された。ま

た、CSPの製造コストの低減を図る目的で、ウェハ状 態のまま複数のCSPを製造する技術が開発されている (特開平8-102466号公報参照)。なお、本明細 書においては、ウェハ状態のCSPを「ウェハレベルC SP」と呼ぶこととする。また、ダイシング等によって 最終的にウェハから切り出されるチップを、ウェハから 切り出される前の状態においても、「チップ」と呼ぶこ ととする。

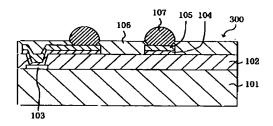

【0004】以下、図9を参照しながら、従来のウェハ レベルCSPを説明する。図9は、従来のウェハレベル CSP300の一部の断面を模式的に示している。図9 ではウェハレベルCSP300の一部を示しているが、 ウェハレベルCSP300は、一枚の半導体ウェハにお いて複数形成されている。

【0005】ウェハレベルCSP300は、半導体ウェ ハ内に形成された半導体チップ101と、半導体チップ 101の主面に配列された素子電極(電極パット)10 3と、半導体チップ101の主面上に形成されたパッシ ベーション膜102と、パッシベーション膜102上に 形成され、素子電極103に電気的に接続されたA1配 線層104およびNiメッキ層105とを有している。 Niメッキ層105の一部には、半田バンプ107が接 合されており、パッシベーション膜102上には、A1 配線層104およびNiメッキ層105を被覆し、且つ 半田バンプ107の一部を露出するカバーコート膜10 6が形成されている。

【0006】次に、従来のウェハレベルCSP300の 製造方法を説明する。まず、複数の半導体チップ101 が形成された半導体ウェハを用意した後、スピンコート 法を用いて半導体ウェハ上にパッシベーション膜102 を形成する。次に、周知の露光技術およびエッチング技 術によって、半導体チップ101の主面上に位置する素 子電極103を露出する開口部をパッシベーション膜1 02に形成する。次に、露出した素子電極103に一端 が電気的に接続されたA1配線層104をパッシベーシ ョン膜102上に形成する。

【0007】次に、マスクを用いてスパッタなどの薄膜 形成技術により、A1配線層104上にNiメッキ層1 05を形成する。次に、A1配線層104およびNiメ ッキ層105を被覆するカバーコート膜106をパッシ ベーション膜102上に形成する。次に、半田バンプ1 07の接合部位を露出する開口部をパッシベーション膜 102に格子状に複数個形成した後、露出した接合部位 に半田バンプ107を接合する。このようにして従来の ウェハレベルCSP300は製造される。ウェハレベル CSP300のそれぞれを分離すれば、CSPが得られ る。

[0008]

【発明が解決しようとする課題】しかしながら、従来の ウェハレベルCSP300には、次のような問題があ る。すなわち、ウェハレベルCSP300を分離して得 られるCSPは、半導体チップ101の側面および裏面 が露出しているため、機械的な衝撃によってチッピング が起こりやすく、信頼性が乏しい。

【0009】本発明はかかる諸点に鑑みてなされたもの であり、その主な目的は、機械的な衝撃から半導体チッ プを保護することができ、信頼性を向上させた半導体装 置およびその製造方法を提供することにある。

[0010]

【課題を解決するための手段】本発明による半導体装置

は、素子電極が配列された主面と前記主面の外縁を規定 する側面とを有する半導体素子と、前記半導体素子の前 記主面上および前記半導体素子の前記側面上に形成さ れ、前記素子電極を露出する開口部を有する絶縁層と、 前記絶縁層上に形成され、前記開口部内において前記素 子電極と電気的に接続された配線層と、前記配線層の一 部として前記絶縁層上に形成された外部電極とを備え、

これにより上記目的が達成される。

【0011】前記半導体素子の前記主面に対向する裏面 上に形成された樹脂層をさらに有することが好ましい。 【0012】前記絶縁層および前記樹脂層は、同一の絶

縁性樹脂材料から形成されていることが好ましい。 【0013】前記樹脂層は、導電性樹脂層であってもよ

い。前記導電性樹脂層は、前記素子電極の一部に電気的 に接続されていることが好ましい。

【0014】前記樹脂層は、前記半導体素子の前記裏面 の一部を露出する開口部を有していることが好ましい。

【0015】前記樹脂層は絶縁性樹脂層であり、前記絶 縁性樹脂層上に形成された金属層をさらに備えることが 好ましい。

【0016】ある実施形態では、前記配線層は、前記側 面上に位置する絶縁層上に形成された側面配線層を有

し、前記金属層は、前記側面配線層に電気的に接続され ている。 前記金属層は、一部が外部電極として機能す る金属配線層であることが好ましい。

【0017】前記外部電極に接合された金属ボールをさらに有することが好ましい。

【0018】前記外部電極上に形成された導電性突起を さらに有していてもよい。

【0019】ある実施形態では、前記半導体素子の前記 主面に形成され、前記素子電極を露出する開口部を有す るパッシベーション膜をさらに備え、前記絶縁層は、前 記パッシベーション膜上に形成されている。

【0020】前記半導体素子は、半導体ウェハ内に形成 された半導体チップであってもよいし、前記半導体素子 は、半導体ウェハから分離された半導体チップであって もよい。

【0021】本発明による半導体装置の製造方法は、素 子電極が配列された主面を有する複数の半導体素子が形 成された半導体ウェハを用意する工程と、前記複数の半 導体素子のそれぞれの前記主面の外縁を規定する側面を 露出する溝を前記半導体ウェハに形成する工程と、前記 溝内に露出した前記側面と前記主面との上に、前記素子 電極を露出する開口部を有する絶縁層を形成する工程

と、前記開口部に露出した前記素子電極に電気的に接続 される配線層であって、その一部が外部電極として機能 する配線層を、前記絶縁層上に形成する工程と、前記主 面に対向する裏面を研磨することによって、前記側面上 に形成された絶縁層を前記裏面から露出させる工程とを 包含し、これによって上記目的を達成する。 【0022】研磨された前記裏面に樹脂層を形成する工 程をさらに包含することが好ましい。

【0023】ある実施形態では、前記半導体素子の前記 主面を保護するために使用するバックグラインドテープ を前記主面に接着させた後、前記半導体素子の前記裏面 を研磨し、前記バックグラインドテープを前記主面に接 着させた前記半導体素子の前記裏面に前記樹脂層を形成 する。

【0024】ある実施形態では、前記半導体素子の前記 主面を保護するために使用するプレートを前記主面に接 着剤を介して接着させた後、前記半導体素子の前記裏面 を研磨し、前記プレートを前記主面に接着させた前記半 導体素子の前記裏面に前記樹脂層を形成する。

【0025】前記絶縁層および前記樹脂層を同一の絶縁 性樹脂材料から形成することが好ましい。

【0026】前記樹脂層として導電性樹脂層を形成して もよい。

【0027】前記樹脂層に、前記裏面の一部を露出する 開口部を形成する工程をさらに包含してもよい。

【0028】ある実施形態では、前記配線層として、前 記半導体素子の前記側面上に位置する絶縁層上に形成さ れる側面配線層を有する配線層を形成し、前記裏面を研 磨することによって、前記側面配線層を前記裏面から露 出させ、前記裏面に形成する樹脂層として、前記側面配 線層を露出する開口部を有する絶縁性樹脂層を形成し、

前記開口部内に露出した前記側面配線層に電気的に接続 される金属層を前記絶縁性樹脂層上に形成する。

【0029】前記金属層として、一部が外部電極として 機能する金属配線層を形成することが好ましい。

【0030】前記配線層を形成する工程の後に、前記絶 線層上に形成され、前記配線層を被覆し、且つ前記外部 電極の一部を露出するソルダーレジスト層を形成する工 程をさらに包含することが好ましい。

【0031】前記金属配線層を形成する工程の後に、前 記絶縁性樹脂層上に形成され、前記金属配線層を被覆

し、且つ前記外部電極の一部を露出するソルダーレジス ト層を形成する工程をさらに包含することが好ましい。 【0032】前記外部電極上に金属ボールを接合する工 程をさらに包含することが好ましい。

【0033】前記外部電極上に導電性突起を形成する工 程をさらに包含してもよい。

【0034】ある実施形態では、前記裏面から絶縁層を 露出させる工程より後に、前記半導体ウェハを前記複数 の半導体素子のそれぞれに分離する工程をさらに包含す る。

[0035]

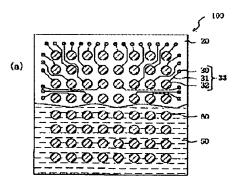

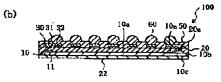

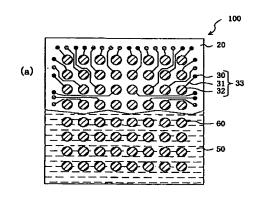

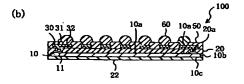

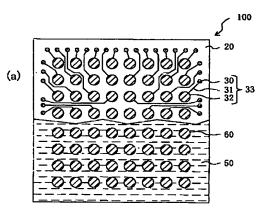

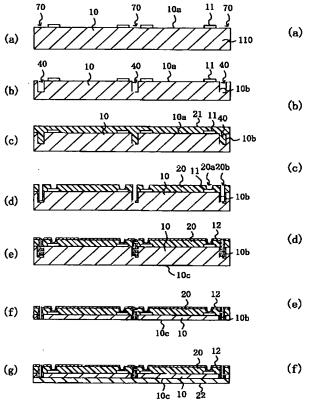

【発明の実施の形態】以下、図面を参照しながら本発明 の実施形態を説明する。以下の図面においては、簡単さ のために、実質的に同一の機能を有する構成要素を同一 の参照符号で示す。 (実施形態1)図1から図4を参照しながら、本発明に よる実施形態1を説明する。図1(a)は、本実施形態 にかかる半導体装置100の上面を一部切り欠いて模式 的に示している。図1(b)は、半導体装置100の断 面を模式的に示している。本実施形態の半導体装置1 00は、半導体素子10と、半導体素子10の主面10 a上に配列された素子電極11と、主面10a上および 主面10aの外縁を規定する側面10b上に形成された 絶縁層20と、主面10aに対向する裏面10c上に形 成された樹脂層22と、絶縁層20上に形成された配線 層33とを備えている。

【0036】配線層33は、素子電極11に接合された コンタクト部30と、外部機器に電気的に接続可能なラ ンド32と、コンタクト部30とランド32とを電気的 に接続する配線31とを有している。ランド32は、外 部機器と半導体素子10との間で伝達される信号の入出 力を行う外部電極として機能し、半導体素子10の主面 10a上に二次元的に配置されている。ランド32は、 配線層33の一部として形成されており、コンタクト部 30、配線32およびランド32は、同一金属(例え

ば、銅)から形成され得る。

【0037】絶縁層20上には、配線層33を被覆し且 つランド32の一部を露出するソルダーレジスト層50 が形成されており、ランド32には、外部電極端子とし て機能する金属ボール60が接合されている。ランド3 2に金属ボール60が接合されていると、簡便なプロセ スで迅速に、金属ボール60を介してランド32と配線 基板(プリント基板)とを電気的に接続することができ る。金属ボール60は、例えば、半田、半田メッキされ た銅、ニッケル等から構成されている。

【0038】半導体素子10は、例えば半導体チップで あり、トランジスタ等を含む半導体集積回路部(不図 示)を備えており、半導体集積回路部は素子電極11と 電気的に接続されている。半導体集積回路部を保護する ため、半導体素子10の主面10aには、素子電極11 を露出する開口部を有するパッシベーション膜(不図 示)が形成されていることが好ましい。本実施形態で は、半導体チップの主面10aの外周部に素子電極が配 置されている。

【0039】また、本実施形態では、半導体素子10の 側面10bは、主面10aとなす角が鈍角(100度程 度)をなすよう傾斜して形成されている。半導体素子1 0の側面10bが傾斜していることによって、製造工程 において側面10b上に塗布される絶縁性樹脂材料の濡 れやすさを向上させることができる。さらに、半導体素 子10の裏面10cは研磨されており、そのため半導体 素子10の厚さ(例えば、150µm程度)は、従来の CSPの厚さ(例えば、500µm程度)よりも薄くな っている。半導体素子10の厚さを薄くすることによっ て、半導体装置100全体の見掛けの熱膨張係数(線膨 張係数)を、半導体素子10の熱膨張係数よりも、絶縁 層20および樹脂層22を構成している材料(例えば、 絶縁性樹脂材料)の熱膨張係数の方に近づけることがで きる。このため、半導体装置10を配線基板に実装した 後、配線基板との接続部に発生する応力を低減すること が可能となる。

【0040】なお、本実施形態では半導体素子10とし て半導体チップを用いているが、半導体チップに分離す る前の半導体ウェハを用いてもよい。また、素子電極1 1が配置される領域(電極配置領域)は、半導体チップ の主面10aの外周部の全ての辺に設けられている必要 はない。また、電極配置領域を主面10aの外周部に設 けずに、例えば主面10aの中央部に設けることも可能 である。なお、素子電極11上に耐メッキ液性を有する バリアメタルを形成することもできる。

【0041】絶縁層20は、主面10a上に加えて、側 面10b上にも形成されている。従って、絶縁層20に よって、従来のCSPでは保護されていなかった半導体 素子10の側面10bを保護することができる。本実施 形態では、側面10b全面に絶縁層20が形成されてい る。主面10a上の絶縁層20の厚さは、配線基板との 接合部に発生する応力の緩和という観点から、例えばう ~100µm程度の範囲内、好ましくは30µm程度で ある。側面10b上の絶縁層20の厚さは、絶縁性の観 点から、例えば3~20µm程度の範囲内、好ましくは 5µm程度である。なお、側面10bの保護の観点から 実質的に影響がない場合、側面10b全面に樹脂層20 が形成されてなくとも、絶縁層20によって側面10b が実質的に被覆されていると言えるので、側面10bの 一部に絶縁層20が形成されていない領域が存在してい てもよい。

【0042】絶縁層20は、絶縁性を有する材料から構 成されており、例えば、エステル結合型ボリイミドやア クリレート系エボキシ等の高分子材料から構成されてい る。絶縁層20は、単一層に限定されず、複数の層(ま たは複数の部分)から形成されていてもよい。例えば、 絶縁層20のうち主面10a上の部分と側面10b上の 部分とを異なる材料から形成することも可能である。な お、同一材料を用いて単一層として形成した場合、絶縁 層20全体が同一の熱膨張係数を有することを防止するこ とができる。

【0043】また、絶縁層20は、絶縁性の弾性材料から構成されていることが好ましい。低弾性率材料(弾性 率が例えば2000kg/mm<sup>2</sup>以下の材料)から構成 した場合、配線基板(プリント基板)と半導体素子10 との間に熱膨張係数の違いに起因して発生する熱応力を 絶縁層20によって緩和することができる。低弾性率材 料として、例えば、エステル結合型ポリイミドやアクリ レート系エポキシ等の高分子材料を用いることができ る。

【0044】絶縁層20は、素子電極11を露出する開 口部20aを有している。開口部20a内において素子 電極11と配線層33とが電気的に接続されている。配 線層33の断線防止の観点より、開口部20aを規定す る側面と絶縁層20の上面とが鈍角(例えば、100~ 150度程度)をなすように開口部20aが形成されて いることが好ましい。

【0045】半導体素子の裏面10c上に形成された樹 脂層22は、例えば、絶縁性を有する樹脂材料から構成 されており、具体的には、エステル結合型ポリイミドや アクリレート系エポキシ等の高分子材料から構成されて いる。樹脂層22を低弾性率材料から構成することもで きる。なお、樹脂層22は、単一層に限定されず、複数

の層(または複数の部分)から形成されていてもよい。 【0046】絶縁層20と樹脂層22とは、同一の絶縁 性樹脂材料から形成されていることが好ましい。両層が 同一材料から形成された場合、両層の硬化収縮や熱膨張 係数が等しくなるため、絶縁性樹脂材料の硬化収縮や熱 膨張によって生じる半導体素子10の反りを抑制・防止 することができる。その結果、半導体装置100の実装 面の平坦性を確保することができ、検査時および実装時 に容易かつ確実に電気的接続が可能な半導体装置100 を提供することができる。半導体素子10の反りをさら に効果的に抑制・防止するため、樹脂層22の厚さは、 絶縁層20の厚さと同程度にすることが好ましい。樹脂 層22の厚さは、例えば5~100µm程度の範囲内、 好ましくは30µm程度にする。

【0047】樹脂層22は、半導体素子の裏面10cの 一部を露出する開口部を有してもよい。樹脂層22が開 口部を有していると、半導体装置100が吸湿したとき にリフローを行っても、吸湿した水分を開口部から水蒸 気として放出させることができるため、水蒸気爆発など の発生を防止することができる。開口部の形状は例えば 円形や矩形であり、具体的には、直径0.2mm φの円 形や寸法0.2×0.2mmの矩形の開口部が複数個

(例えば50個程度)形成されていればよい。吸湿した 水分を水蒸気として放出させる目的のため、開口部の総 面積は、半導体素子の裏面10cの面積の1~5%程度 であることが好ましい。開口部は、例えば、公知のフォ トリソグラフィ技術およびエッチング技術、またはレー ザを用いて形成すればよい。

【0048】本実施形態の半導体装置100では、半導体素子の側面10bが絶縁層20によって被覆されてい るので、物理的な衝撃を緩和して半導体素子の側面10 bを保護することができ、その結果、半導体素子10の チッピングを防止することができる。半導体素子の裏面 10c上に樹脂層22を形成すると、半導体素子の裏面 10cも保護することができる。従って、信頼性に優れ た半導体装置を提供することができる。 【0049】また、主面10a上に絶縁層20が形成さ れているので、ランド32を二次元的に配置することが でき、狭い面積に多数の外部電極を設けることが可能と なる。従って、多ピン化に対応可能な半導体装置(CS P)を提供することができる。さらに、半導体装置10 0はウェハレベルCSPとして製造可能な構成をしてお り、加えて、ランド32を配線層33の一部として形成 することができる構成をしているので、製造コストが極 めて低い半導体装置を提供することができる。

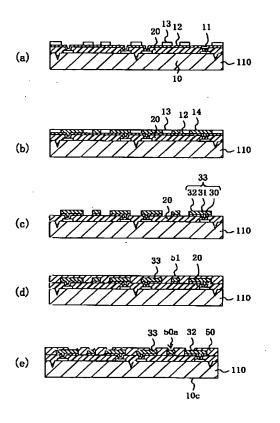

(実施形態2)次に、図2(a)~(e)、図3(a)

~(e)および図4(a)~(e)を参照しながら、実施形態2にかかる半導体装置100の製造方法を説明する。

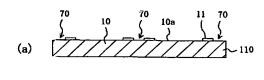

【0050】まず、図2(a)に示すように、複数の半 導体チップ10が形成された半導体ウェハ110を用意 する。複数の半導体チップ10のそれぞれは、素子電極 11が配列された主面10aを有している。なお、半導 体チップ10の主面および裏面は、それぞれ、半導体ウ ェハ110の主面および裏面を意味する場合がある。

【0051】半導体ウェハ110には、複数の半導体チ ップ10のそれぞれを分割するスクライブレーン70が 形成されている。半導体ウェハ110の厚さは、例えば 625µm程度であり、スクライブレーン70の幅は、 例えば80µm程度である。半導体ウェハ110の主面 には、予めパッシベーション膜(不図示)が形成されて いることが好ましい。

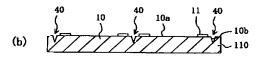

【0052】次に、図2(b)に示すように、複数の半 導体チップ10のそれぞれの主面10aの外縁を規定す る側面10bを露出する溝40を半導体ウェハ110に 形成する。例えば、ダイシングソーを用いて半導体ウェ ハ40の主面側からスクライブレーン70に沿って溝4 0を形成する。溝40の幅は、例えば100µm程度で あり、溝40の深さは、例えば300µm程度である。 主面10aと側面10bとが鈍角(例えば100度程 度)をなすようにV字型に溝は形成される。V字型に溝 を形成すると、後の工程で側面10b上に塗布される絶 縁性樹脂材料の濡れやすさを向上させることができる。 なお、V字型に代えて、凹字型の溝を形成してもよい。 溝40の形成方法は、レーザやプラズマによる機械的な 加工、またはエッチングなどの化学的な加工によって行 ってもよい。

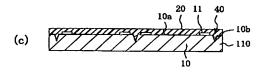

【0053】次に、図2(c)に示すように、溝40内 に露出した側面10bと主面10aとの上に絶縁層20 を形成する。本実施形態では、側面10b全面に絶縁層 20を形成する。絶縁層20の形成は、例えば、感光性 絶縁材料を塗布した後、乾燥することによって行う。絶 縁層20の厚さは、例えば5~15µm程度、好ましく は10µm程度にする。

【0054】次に、図2(d)に示すように、素子電極 11を露出する開口部20aを絶縁層20に形成する。 開口部20aの形成は、絶縁層20を露光・現像するこ とによって行う。開口部20aを形成する場合、露光工 程において平行光ではなく例えば拡散光(散乱光を含 む)を使用することが好ましい。拡散光を使用すること によって、開口部の側面と絶縁層20の上面とが鈍角 (例えば、100~140度程度)をなすように、開口 部20aを形成することができる。

【0055】絶縁層20を形成するための感光性絶縁材 料としては、例えばエステル結合型ボリイミドやアクリ レート系エボキシ等の高分子材料を用いることができ、 絶縁性を有する材料であれば特に限定されない。なお、 感光性絶縁材料は液状である必要はなく、予めフィルム 状に形成された材料を用いてもよい。この場合、フィル ム状の感光性絶縁材料を半導体素子10上に貼りあわせ た後に、露光と現像とを順次行って開口部20aを形成 することができる。また、感光性を有していない絶縁材 料を用いることも可能である。この場合、例えば、レー ザやプラズマを用いる機械的な加工、またはエッチング などの化学的な加工によって開口部20aを形成すれば よい。

【0056】次に、図2(e)に示すように、絶縁層2 Oおよび素子電極11の上に薄膜金属層12を形成す る。薄膜金属層12の形成は、真空蒸着法、スパッタリ ング法、CVD法、または無電解めっき法を用いて、例 えば、Ti膜(厚さ:0.2µm程度)を堆積した後、 Ti膜上にCu膜(厚さ:0.5µm程度)を堆積する ことによって行う。

【0057】次に、図3(a)に示すように、薄膜金属 層12の上にメッキレジスト膜13を形成する。メッキ レジスト膜13の形成は、薄膜金属層12上にポジ型感 光性レジストを塗布した後、このレジストのうち仕上げ 製品の所望のパターン部の部分を分解し、次いで所望の パターン部を除去することによって行う。なお、ポジ型 感光性レジストに代えて、ネガ型感光性レジストを用い てメッキレジスト膜13を形成してもよい。

【0058】次に、図3(b)に示すように、メッキレ ジスト膜13の形成された部分以外の薄膜金属層12上 に厚膜金属層14を形成する。厚膜金属層14の形成 は、例えば電解めっき法を用いて行う。厚膜金属層14

の厚さは、例えば5µm~15µmの範囲内、好ましく は10µm程度にする。電解めっき法を用いると、他の 方法よりも短時間で厚膜を形成することができるという 利点がある。

【0059】次に、図3(c)に示すように、メッキレ ジスト膜13を分解除去した後、薄膜金属層12を選択 的に除去することによって、コンタクト部30、配線3 1およびランド32から構成される配線層33を形成す る。薄膜金属層12を溶解できるエッチング液(例え

ば、Cu膜に対して塩化第二銅溶液、Ti膜に対してE DTA溶液)を用いて全面エッチングを行うと、厚膜金 属層14よりも厚さの薄い薄膜金属層12が先行して除 去されるので、薄膜金属層12を選択的に除去すること ができる。

【0060】次に、図3(d)に示すように、感光性ソ ルダーレジスト材料51を絶縁層20の上に堆積する。 その後、図3(e)に示すように、配線層33のランド 32の少なくとも一部を露出する開口部50aを感光性 ソルダーレジスト材料51にフォトリソグラフィ技術を 用いて形成し、ソルダーレジスト層50を得る。ソルダ ーレジスト層50を形成することによって、コンタクト 部30と金属配線31を溶融したはんだから保護するこ とができる。

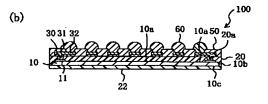

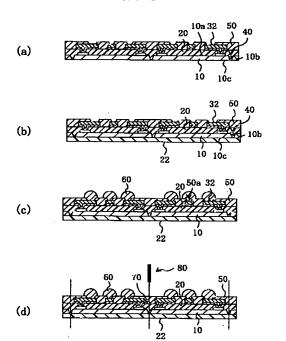

【0061】次に、図4(a)に示すように、半導体チ ップ(または半導体ウェハ)の主面10aに対向する裏 面10cを研磨することによって、側面10b上に形成 された絶縁層20(溝40内の絶縁層20)を裏面10 cから露出させる。研磨後の半導体チップ10の厚さは 300μm程度である。

【0062】裏面10cの研磨は、半導体ウェハ101 の主面10aを保護するために使用するバックグライン ドテープ(不図示)を主面10aに接着させた後に実行 することが好ましい。裏面10cを研磨した後は、絶縁 層20の残留応力によって、樹脂層20側が凹になるよ うに半導体ウェハ10が反るため、この反りをバックグ ラインドテープによって防ぐことが望ましいからであ る。バックグラインドテープとしては、厚さが100μ m以上であり、ヤング率が200kg/cm<sup>2</sup>以上ある ことが好ましい。

【0063】また、バックグラインドテープの代わり に、プレート(例えば、シリコン基板やセラミック基 板)を接着剤を介して主面10aに接着させた後、裏面 10cの研磨を行っても良い。この場合、一定温度で接 着性がなくなるように設計された接着剤を用いることが 好ましい。

【0064】次に、図4(b)に示すように、研磨され た裏面10c上および裏面10cから露出した絶縁層2 0上に、すなわち、半導体ウェハ110の裏面10c上 に樹脂層22を形成する。樹脂層22の形成は、例え

ば、絶縁性樹脂材料を塗布した後、乾燥することによっ て行う。樹脂層22を形成する材料として、絶縁層20 と同一の材料を用いることが好ましい。両層を同一材料 から形成することによって、両層の硬化収縮や熱膨張係 数を等しくすることができ、絶縁性樹脂材料の硬化収縮 や熱膨張によって生じる半導体ウェハ101(または半 導体チップ10)の反りを抑制・防止することができる からである。また、同一材料を用いれば、材料コストの 低減を図ることもできる。半導体ウェハ110の反りを さらに効果的に抑制・防止するため、樹脂層22の厚さ を、絶縁層20の厚さと同程度にすることが望ましい。 樹脂層22の厚さは、例えば5~100µm程度の範囲 内、好ましくは30µm程度にする。

【0065】樹脂層22の形成は、バックグラインドテ ープまたはプレートを主面10aに接着させた状態で行 うことが好ましい。このようにすれば、半導体ウェハ1 01が複数の半導体チップ10のそれぞれに分離するこ とを防止することができるため、半導体ウェハ101の 裏面全面に樹脂層22を形成でき、製造効率を向上させ ることができるからである。

【0066】次に、図4(c)に示すように、開口部5 0 a内に露出したランド32上に金属ボール60を載置 した後、ランド32と金属ボール60とを溶融結合させ る。

【0067】最後に、図4(d)に示すように、半導体 ウェハ101のスクライブレーン70に沿って、例えば 30µm幅のダイシングソーを用いてダイジングを行う と、図4(e)に示すように、半導体ウェハ101から 半導体チップ10のそれぞれが分離され、半導体装置1 00が得られる。

【0068】本実施形態によれば、半導体ウェハ101 の裏面10cを研磨し、溝40内の絶縁層20を裏面1 0cから露出させることによって、半導体チップ10の 側面10bを樹脂層20で被覆した半導体装置(また

は、ウェハレベルCSP)を簡便なプロセスで製造する ことができる。また、配線層33の一部としてランド3 2を形成することができるので、製造工程の削減を図る ことができる。

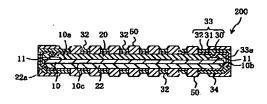

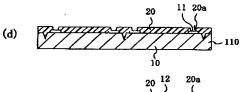

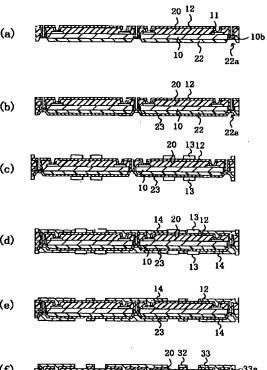

(実施形態3)図5を参照しながら、本発明による実施 形態3を説明する。図5は、本実施形態にかかる半導体 装置200の断面を模式的に示している。本実施形態の 半導体装置200は、樹脂層22上に金属配線層32を 有している点において、実施形態1の半導体装置100 と異なる。本実施形態の説明を簡明にするため、以下で は、実施形態1と異なる点を主に説明し、実施形態1と 同様の点の説明は省略する。

【0069】半導体装置200は、半導体チップ(半導 体素子)10と、半導体チップ10の主面10a上およ び側面10b上に形成された絶縁層20と、裏面10c 上に形成された絶縁性樹脂層22と、絶縁層20上に形 成された配線層33と、絶縁性樹脂層22上に形成され た金属配線層34を備えている。配線層33および金属 配線層34は、外部電極として機能するランド32を有 しており、絶縁層20上および絶縁性樹脂層22上に は、配線層33および金属配線層34を被覆し、且つラ ンド32の一部を露出するソルダーレジスト層50が形 成されている。

【0070】絶縁層20上に形成された配線層33は、 半導体素子10の側面上に位置する絶縁層上に形成され た側面配線層33aを有している。側面配線層33a は、主面10a上に配列された複数の素子電極11の一 部に電気的に接続されている。また、側面配線層33a は、絶縁性樹脂層22上に形成された金属配線層34に 電気的に接続されている。側面配線層33aに電気的に 接続された金属配線層34の断線を防止するために、絶 縁性樹脂層22の側面22aはテーパー状に形成されて いることが好ましい。側面配線層33aは、例えば、配 線層33と同一の材料から形成されており、側面配線層 33aの厚さは、例えば3~20µm程度であり、5µ m程度であることが好ましい。

【0071】本実施形態の半導体装置200は、半導体 チップ10の裏面10c上に金属配線層34を有してい るので、半導体チップ10の熱を金属配線層34に伝え て放熱させることができる。このため、放熱性に優れた 半導体装置を提供することができる。また、金属配線層 34が側面配線層33aに電気的に接続されているの

で、半導体チップ10を電気的にシールドした構造にす ることができる。従って、電磁シールド性に優れた半導 体装置を提供することができる。その結果、半導体装置 の信頼性を向上させることが可能となる。

【0072】さらに、半導体装置200では、半導体チ ップ10の主面10aおよび裏面10cの両面上にラン ド32が形成されているので、半導体装置200の両面 を利用して3次元的な実装をすることが可能である。ま た、半導体チップ10の側面10bおよび裏面10cが 絶縁層20および絶縁性樹脂層22によって保護されて いるので、実施形態1の半導体装置100と同様に、チ ッピングの発生を防止することができる。

【0073】本実施形態では、絶縁性樹脂層22上に金 属配線層34が形成されているが、放熱性の向上という 観点から、金属配線層34に代えて、単に金属層が形成 されていてもよい。この金属層を側面配線層33aに電 気的に接続した構造にすれば、半導体チップ10を電気 的にシールドすることができるため、電磁シールド性を 向上させることができる。

【0074】また、金属配線層34および絶縁樹脂層2 2に代えて、半導体チップ10の裏面10cに導電性樹 脂層を形成した構成にすることも可能である。裏面10 cに形成した導電性樹脂層によって、半導体素子の放熱 性を向上させることができ、この導電性樹脂層と素子電 極11の一部とを、例えば側面配線層33aを介して相 互に接続すれば、電磁シールド性を向上させることがで きる。導電性樹脂層は、例えば、炭素(微粒子)、銅ま たはニッケル等の導電性フィラーを含む樹脂材料から形 成することができ、高熱伝導性を有する樹脂層である。 また、放熱性の向上を主目的とするならば、アルミナま たは窒化アルミナ等の高熱伝導性を示す絶縁フィラーを 含む樹脂材料から形成した絶縁性樹脂層を、導電性樹脂 層に代えて、形成することも可能である。

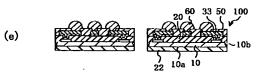

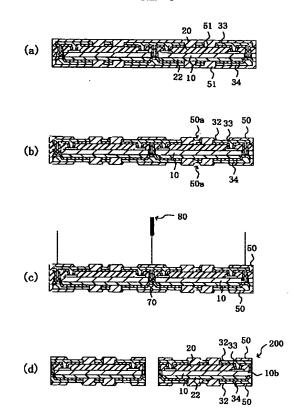

(実施形態4)次に、図6(a)~(g)、図7(a) ~(f)および図8(a)~(d)を参照しながら、実 施形態4にかかる半導体装置200の製造方法を説明す る。本実施形態の説明を簡明にするため、以下では、実 施形態2と異なる点を主に説明し、実施形態2と同様の 点の説明は省略する。

【0075】まず、図6(a)に示すように、複数の半 薄体チップ10が形成された半導体ウェハ110を用意 した後、図6(b)に示すように、複数の半導体チップ 10の側面10bを露出する溝40を半導体ウェハ11 0に形成する。本実施形態では、スクライブレーン70 に沿って、凹型の溝40(幅:100µm程度、深さ: 300µm程度)を形成する。なお、凹型に代えて、V 字型の溝を形成してもよい。

【0076】次に、図6(c)に示すように、溝40内 に露出した側面10bと主面10aとの上に絶縁層20 を形成する。絶縁層20の厚さは、例えば5~100μ m程度、好ましくは30μm程度にする。

【0077】次に、図6(d)に示すように、素子電極 11を露出する開口部20aと、側面10b上に形成さ れた絶縁層20を溝40内に露出する開口部20bとを 絶縁層20に形成する。開口部20aおよび開口部20 bの形成は、絶縁層20を露光・現像することによって 行う。

【0078】次に、図6(e)に示すように、半導体チ ップの主面10aおよび側面10b上に位置する絶縁層 20と、素子電極11との上に薄膜金属層12を形成す る。薄膜金属層12の形成は、真空蒸着法、スパッタリ ング法、CVD法、または無電解めっき法を用いて、例 えば、Ti膜(厚さ:0.2 $\mu$ m程度)を堆積した後、 Ti膜上にCu膜(厚さ:0.5 $\mu$ m程度)を堆積する ことによって行う。なお、スパッタリング法で堆積を行 う場合、図6(a)の工程でV字型の溝を形成して影が できないにすると、蒸着しやすくできる。このとき、ス

パッタリング法による堆積が好ましくなければ、指向性 の少ない電子ビーム蒸着法やCVD法を用いることがで きる。

【0079】次に、図6(f)に示すように、半導体チ ップ(または半導体ウェハ)の裏面10cを研磨するこ とによって、側面10b上に形成された絶縁層20およ び薄膜金属層12(溝40内の絶縁層20および薄膜金 属層12)を裏面10cから露出させる。研磨後の半導 体チップ10の厚さは150 $\mu$ m程度である。研磨の際 には、半導体チップ10の反りを防止するために、バッ クグラインドテープ(厚さ:100 $\mu$ m以上、ヤング 率:200kg/cm<sup>2</sup>以上)、または接着剤を介して プレート(例えば、シリコン基板やセラミック基板)を 主面10aに接着することが好ましい。

【0080】次に、図6(g)に示すように、研磨され た裏面10c上と、裏面10cから露出した絶縁層20 および薄膜金属層12の上に、すなわち、半導体ウェハ 110の裏面上に樹脂層22を形成する。樹脂層22の 形成は、例えば、感光性絶縁樹脂材料を塗布した後、乾 燥することによって行う。実施形態2と同様の理由によ り、樹脂層22を形成する材料は、絶縁層20と同一の 材料を用いることが好ましい。また、樹脂層22の厚さ は、絶縁層20の厚さと同程度にすることが望ましい。 樹脂層22の厚さは、例えば5~100µm程度の範囲 内、好ましくは30µm程度にする。

【0081】次に、図7(a)に示すように、研磨によって露出した溝40内の絶縁層20および薄膜金属層1 2を露出する開口部22aを樹脂層22に形成する。開 口部22aの形成は、樹脂層22を露光・現像すること によって行う。開口部22aを形成する場合、露光工程 において平行光ではなく例えば拡散光(散乱光を含む) を使用することが好ましい。拡散光を使用することによって、開口部の側面と樹脂層22の上面とが鈍角(例え ば、100~140度程度)をなすように、開口部22 aを形成することができる。このようにテーパー状に開 口部22aを形成することによって、後の工程で形成さ れる金属配線層34の断線を防止することができる。

【0082】次に、図7(b)に示すように、樹脂層2 2と、開口部22a内に露出した絶縁層20および薄膜 金属層12との上に、薄膜金属層23を形成する。薄膜 金属層23の形成は、真空蒸着法、スパッタリング法、 CVD法、または無電解めっき法を用いて、例えば、T i膜(厚さ:0.2 $\mu$ m程度)を堆積した後、Ti膜上 にCu膜(厚さ:0.5 $\mu$ m程度)を堆積することによ って行う。

【0083】次に、図7(c)に示すように、薄膜金属 層12および23の上にメッキレジスト膜13を形成す る。メッキレジスト膜13の形成は、薄膜金属層12お よび23上にポジ型感光性レジストを塗布した後、この レジストのうち仕上げ製品の所望のパターン部の部分を 分解し、次いで所望のパターン部を除去することによっ て行う。なお、ポジ型感光性レジストに代えて、ネガ型 感光性レジストを用いてメッキレジスト膜13を形成し てもよい。

【0084】次に、図7(d)に示すように、メッキレ ジスト膜13の形成された部分以外の薄膜金属層12お よび23上に厚膜金属層14を形成する。厚膜金属層1 4の形成は、例えば電解めっき法を用いて行う。厚膜金 属層14の厚さは、例えば5μm~15μmの範囲内、 好ましくは10μm程度にする。

【0085】次に、図7(e)に示すように、メッキレ ジスト膜13を分解除去する。その後、図7(f)に示 すように、薄膜金属層12および23を選択的に除去す ることによって、側面配線層33aを有する配線層33 と、金属配線層34とを形成する。薄膜金属層12およ び23を溶解できるエッチング液(例えば、Cu膜に対 して塩化第二銅溶液、Ti膜に対してEDTA溶液)を 用いて全面エッチングを行うと、厚膜金属層14よりも 厚さの薄い薄膜金属層12および23が先行して除去さ れるので、薄膜金属層12を選択的に除去することがで きる。配線層33および金属配線層34の両層とも、外 部電極として機能するランド32を備えている。

【0086】次に、図8(a)に示すように、感光性ソ ルダーレジスト材料51を絶縁層20および22の上に 堆積する。その後、図8(b)に示すように、配線層3 3と金属配線層34との両層のランド32の少なくとも 一部を露出する開口部50aを感光性ソルダーレジスト 材料51にフォトリソグラフィ技術を用いて形成し、ソ ルダーレジスト層50を得る。

【0087】最後に、図8(c)に示すように、半導体 ウェハ101のスクライブレーン70に沿って、例えば 30µm幅のダイシングソーを用いてダイジングを行う と、図8(d)に示すように、半導体ウェハ101から 半導体チップ10のそれぞれが分離され、半導体装置2 00が得られる。なお、ランド32に金属ボールを載置 して溶融接合させてもよい。

【0088】本実施形態では、半導体ウェハ110裏面 の研磨によって側面配線層33aを裏面10cから露出 させた後、裏面10cから露出した側面配線層33aに 電気的に接続される金属配線層34を形成する。このた め、放熱性および電磁シールド性に優れ、且つ3次元実 装可能な半導体装置(または、ウェハレベルCSP)を 簡便なプロセスで製造することができる。

(他の実施形態)上記実施形態では薄膜金属層および厚 膜金属層を構成する材料としてTiおよびCuを使用し たが、これに代えてCr、W、Ti/Cu、Ni等を使 用してもよい。また、薄膜金属層と厚膜金属層とをそれ ぞれ異なる金属材料により構成しておき、最終的なエッ チング工程で薄膜金属層のみを選択的にエッチングする エッチャントを用いてもよい。

【0089】上記実施形態では、金属ボール60を設け たが、これに代えて突起電極を設けてもよい。突起電極 として、例えば、はんだクリームをランド32上に印 刷、溶融することによって形成されたはんだバンプ、溶 融はんだ内にディップすることによって形成されたはん だバンプ、無電解めっきによって形成されたニッケル/ 金バンプなどを設けることができる。突起電極は、導電 性を有し、かつソルダーレジスト層50から突出してい ればよい。突起電極を設けることによって、金属ボール 60を順次搭載する手間の掛かる工程とが不要となるた め、低コストの半導体装置を実現することができる。

【0090】また、ランド32を外部電極端子として機 能させるランド・グリッド・アレイ(LGA)型の構成 を採用してもよい。LGA型の構成を採用した半導体装 置を配線基板上に実装する際には、配線基板の接続端子 の上にはんだクリームを塗布した後リフローさせるなど の方法によって、ランド32と配線基板との電気的な接 続を容易に行なうことができる。 【0091】 【発明の効果】本発明の半導体装置によれば、半導体素 子の側面上に絶縁層が形成されているので、物理的な衝 撃を緩和して半導体素子の側面を保護することができ、 チッピングの発生を防止することができる。その結果、 信頼性に優れた半導体装置を提供することができる。

【0092】半導体素子の裏面上に樹脂層が形成された 場合、半導体素子の裏面を保護することができ、さらに 信頼性を向上させることができる。絶縁層と樹脂層とが 同一の絶縁性樹脂材料から形成されているときには、両 層の硬化収縮や熱膨張係数が等しくなるため、半導体素 子の反りを効果的に抑制・防止することができる。その 結果、半導体装置の実装面の平坦性を確保することがで き、検査時および実装時に容易かつ確実に電気的接続が 可能な半導体装置を提供することができる。

【0093】半導体素子の裏面上に導電性樹脂層が形成 された場合、半導体素子の裏面を保護することができ、 さらに、半導体装置の放熱性を向上させることができ る。導電性樹脂層が素子電極の一部に電気的に接続され ているときには、半導体素子を電気的にシールドした構 造にすることができるため、電磁シールド性に優れた半 導体装置を提供することができる。

【0094】半導体素子の裏面の一部を露出する開口部 を樹脂層に形成した場合には、半導体装置が吸湿したと きにリフローを行っても、吸湿した水分を開口部から水 蒸気として放出させることができるため、水蒸気爆発な どの発生を防止することができる。このため、信頼性に 優れた半導体装置を提供することができる。

【0095】半導体素子の裏面上に金属層が形成された 場合、半導体装置の放熱性を向上させることができる。 金属層が側面配線層に電気的に接続されているときに は、半導体素子が電気的にシールドされた構造にするこ とができ、その結果、電磁シールド性に優れた半導体装 置を提供することができる。また、金属層として金属配 線層が形成されている場合、半導体素子の裏面にある外 部電極によっても外部機器との電気的接続が可能とな る。このため、半導体素子の主面および裏面の両面に実 装可能な半導体装置を提供することができる。

【0096】本発明による半導体装置の製造方法では、 半導体素子の側面上に形成した絶縁層を、裏面を研磨す ることによって裏面から露出させる。これにより、半導 体素子の側面が絶縁層で被覆された構造の半導体装置を 簡便なプロセスで製造することができる。また、裏面に 樹脂層を形成すると、半導体素子の裏面を保護した半導 体装置を製造することができる。

【0097】裏面を研磨する際に、半導体素子の主面に バックグラインドテープを接着させることによって、半 導体素子の反りを防止することができる。また、バック グラインドテープによって、複数の半導体素子がそれぞ れに分離することを防止して、裏面に樹脂層を形成する ことができる。バックグラインドテープの代わりに、プ レートおよび接着剤を使用することもできる。

【0098】側面配線層を有する配線層を形成した後、 側面配線層を裏面の研磨によって裏面から露出させ、裏 面から露出した側面配線層に電気的に接続される金属層 を裏面上に形成すると、放熱性および電磁シールド性に 優れた半導体装置を簡便なプロセスで製造することがで きる。

【0099】裏面から絶縁層を露出させた後に、半導体 ウェハを複数の半導体素子のそれぞれに分離することに よって、半導体チップに分離される前の半導体ウェハを 用いて各工程を行うことができるため、製造コストを大 幅に低減することができる。

【図面の簡単な説明】

【図1】(a)は、実施形態1にかかる半導体装置10 0を一部切り欠いて模式的に示す平面図であり、(b) は、半導体装置100を模式的に示す断面図である。 【図2】(a)~(e)は、実施形態2にかかる半導体 装置の製造方法を説明するための工程断面図である。

【図3】(a)~(e)は、実施形態2にかかる半導体 装置の製造方法を説明するための工程断面図である。

【図4】(a)~(e)は、実施形態2にかかる半導体 装置の製造方法を説明するための工程断面図である。 【図5】実施形態3にかかる半導体装置200を模式的

(因う) 天地があったから十零体表置2002 検式的に示す断面図である。

【図6】(a)~(g)は、実施形態4にかかる半導体 装置の製造方法を説明するための工程断面図である。 【図7】(a)~(f)は、実施形態4にかかる半導体 装置の製造方法を説明するための工程断面図である。 【図8】(a)~(d)は、実施形態4にかかる半導体 装置の製造方法を説明するための工程断面図である。

【図5】

【図9】従来のウェハレベルCSP300を模式的にを 示す断面図である。 【符号の説明】

10 半導体素子(半導体チップ)

- 素子電極(電極パッド)

- 12 薄膜金属層

- 13 メッキレジスト層

- 14 厚膜金属層

- 20 絶縁層

- 22 樹脂層

- 23 薄膜金属層

- 30 コンタクト部

- 31 配線

- 33 配線層

- 33a 側面配線層

- 34 金属配線層

- 40 溝

- 50 ソルダーレジスト層

- 60 金属ボール

- 70 スクライブレーン

- 80 ダイシングソー

- 100、200 半導体装置

- 101、110 半導体ウェハ

- 102 パッシベーション膜

- 103 素子電極(電極パッド)

- 104 Al配線

- 105 Niメッキ層

- 106 カバーコート膜

- 107 半田バンプ

- 300 ウェハレベルCSP

【図1】

۲

٩.

.

【図3】

• •

٩.

【図4】

•

۰.

۰.

【図7】

-

【図8】

フロントページの続き

· · ·

۰.

- (72)発明者 下石坂 望

- 大阪府高槻市幸町1番1号 松下電子工業 株式会社内 (72)発明者 中村 嘉文 大阪府高槻市幸町1番1号 松下電子工業 株式会社内

| (72)発明者 | 隈川   | 隆博                |        |

|---------|------|-------------------|--------|

|         | 大阪府  | 守高槻市幸町1番1号        | 松下電子工業 |

|         | 株式会  | ≹社内               |        |

| (72)発明者 | 渡瀬   | 和美                |        |

|         | 大阪府  | <b>清高槻市幸町1番1号</b> | 松下電子工業 |

|         | 株式会  | ≹社内               |        |

| Fターム(参  | 考) 5 | F044 RR18 RR19    |        |

|         |      |                   |        |